數十年來,超高速且具揮發性的靜態隨機存取記憶體(SRAM)一直用來當作高性能運算架構的嵌入式快取記憶體;在這些架構中,SRAM置於一套緊鄰處理器的多層(L1、L2、L3等等)階層式系統內。其功能是儲存常用資料及快取指令,其中L1是速度最快的快取記憶體。SRAM位元密度的發展已經放緩一段時間了,而記憶體單元越來越容易面臨待機功耗的問題。

自旋軌道力矩(SOT)磁阻式隨機存取記憶體(MRAM)解決方案有幾項優勢,例如待機功耗低、開關或讀寫速度達到GHz等級、漏電小到可略、重複讀寫次數幾乎無上限、可靠度及可擴充性高。基於這些原因,業界目前越來越看重評估SOT-MRAM在嵌入式底層快取記憶體應用作為替代SRAM的潛力方案。

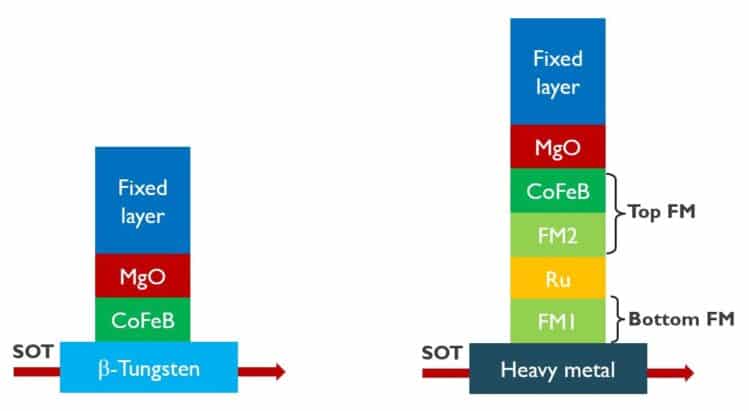

SOT-MRAM記憶體元件的基本構件是磁性穿隧接面(Magnetic Tunnel Junction, MTJ),該接面由一層夾在兩層鈷鐵硼(CoFeB)鐵磁層之間的氧化鎂(MgO)薄介電層組成。其中一層鐵磁層的磁化狀態固定,另一層則在z軸擁有自由旋轉的磁化狀態。這些鐵磁層的磁化方向可以垂直或平行於這些材料層的平面,分別稱為垂直磁性穿隧接面與面內磁性穿隧接面。

SOT-MRAM記憶體單元的讀取方法是施加一股會流經磁性穿隧接面的電流,並測量該接面的穿隧磁阻(Tunnel Magnetoresistance, TMR)。該穿隧磁阻根據自由磁化層和固定磁化層的相對磁化方向(即平行為1,平行但反向為0)而出現高或低數值(圖1)。

圖1 磁阻式隨機存取記憶體(MRAM)穿隧磁阻(TMR)讀取運作的基本原理(上層綠色:固定磁化層,下層綠色:自由磁化層,藍色:氧化鎂介電層,i為讀取電流)。

這些記憶體單元的寫入方法是注入一股自旋極化的電流到該磁性穿隧接面,透過自旋軌道交互作用來切換自由磁化層的磁化狀態。電流在該磁性穿隧接面的下方從橫向注入,並經過一層鄰近的自旋軌道力矩(SOT)層(通常是鎢等重金屬)。這樣一來,讀取和寫入的路徑就完成去耦,確保可靠運作。也是這種寫入運作讓SOT-MRAM異於自旋轉移力矩(STT) MRAM,後者是另一種MRAM,其寫入電流從垂直向注入磁性穿隧接面。在STT-MRAM的寫入期間,大量電流經過氧化鎂(MgO)阻障層。

SOT-MRAM重大突破:免外部磁場實現高可靠度寫入

這幾年,記憶體界已經在開發SOT-MRAM技術方面取得重大進展。imec也憑藉創新的改良技術在這段進程中有所貢獻。自從2018年IEEE國際超大型積體電路技術研討會(VLSI)首次亮相後,imec發布了逐步的創新技術,以應對開發快取應用時所面臨的關鍵挑戰。

目前為止,開關速度最快達到300皮秒(ps)的先進SOT-MRAM單一元件已經展示在12吋晶圓上。採用磁性穿隧接面垂直磁矩曾被認為是提升記憶體微縮發展潛力的重要一步。

透過免除資料寫入期間對外部磁場的需求,SOT-MRAM的技術準備度也取得了進展。為了確保確定性的磁化翻轉,就會需要這種磁場。缺少外部磁場將導致寫入操作的可靠度降低,寫入成功率為50%。從製造面來看,利用外部磁場來操作的記憶體元件,無法在產品層面實現,所以必須開發零場翻轉的SOT-MRAM元件技術。

imec透過整合一層面內磁層作為SOT軌道的一部分,成功展示一種零場翻轉的運作方法。由這層磁層誘發的面內磁場取代了外部磁場的作用,強化這項技術的實際應用性。

至於在降低動態功耗方面,imec也已提出解決方案。SOT-MRAM的動態功耗與翻轉自由磁化層所需的高注入電流有關。在2022年IEEE國際電子會議(IEDM)上,imec展示了一種用於資料寫入期間的電壓閘極輔助法,能夠降低磁翻轉的能障。這種電壓閘極輔助法也能縮小記憶體單元的面積,對高密度SRAM應用來說極具發展潛力。

透過縮小SOT軌道的尺寸,還能進一步改善切換能量。在傳統的SOT-MRAM設計中,為提供堆疊製程控制所需的充足邊距,下層SOT軌道所占據的面積,必須比磁性穿隧接面柱的占板面積還要大。但部分的注入電流會因此傳到磁性穿隧接面的外圍,造成能量浪費。2023年IEDM上,imec展示利用占板面積相當的SOT軌道和磁性穿隧接面柱,提高了SOT-MRAM的微縮潛力。這是邁向高記憶體單元密度的一大里程碑。這些單一元件展示每位元低於100飛焦耳(Femto-Joule)的切換能量,以及超過1015的重複讀寫次數。

後續發展:提升元件性能/可靠度並實現陣列整合

雖然切換速度和重複讀寫次數等關鍵規格已經取得大幅進展,但為了進一步最佳化性能和可靠度參數,例如資料保留時間、後段製程相容性、抗外部磁場影響的防護能力與寫入錯誤率(Write Error Rate, WER),我們必須進一步針對材料堆疊進行改良設計。WER是可靠度的關鍵問題,意指施加寫入電流時,自由鐵磁層並未翻轉的機率。

此外,儘管研究主要關注元件改良,實現業界採用的關鍵一步是微縮SOT-MRAM元件的大型陣列整合。在這些陣列展示元件中,許多記憶體單元目前是連接到下層電路,這些電路包含用來提供讀寫接取的電晶體,以及把電流和電壓傳入和傳出記憶體單元的電晶體。

元件改良和陣列整合將會讓SOT-MRAM技術更貼近現實應用的需求。要處理這些問題,通常需要在不同參數之間做出取捨。imec於2024年IEEE VLSI和IEDM發表的近期研究,著重利用整合最佳化、材料與研究改良設計來盡可能改善這些問題,並藉由模擬來驗證其效果。這項研究的摘要如下。

磁性自由層堆疊創新 強化元件翻轉可靠度

2024年IEDM上,imec提出一套用於磁性穿隧接面的創新複合材料自由層(圖2),藉此提升SOT-MRAM元件的翻轉可靠度。這套新穎的自由層堆疊由一種合成反鐵磁(Synthetic Antiferromagnetic, SAF)結構組成。該結構是兩層經由一層釕(Ru)材料層進行反鐵磁耦合的鐵磁層。隨後,這套系統與傳統的鈷鐵硼層整合,以讀取穿隧磁阻(TMR)。這套創新堆疊可以獨立最佳化穿隧磁阻(對讀取資料來說至關重要)和進行SOT翻轉運作(提供一套用來進一步提升寫入運作效率的方法)。

圖2 傳統的磁性穿隧接面堆疊示意圖(左)與包含合成反鐵磁自由層的磁性穿隧接面堆疊(右)。該合成反鐵磁結構的FM2頂層自由磁性層與鈷鐵硼/氧化鎂進行鐵磁耦合,以利用穿隧磁阻來讀取該合成反鐵磁結構的電性資料(發表於2024年IEEE國際電子會議)。

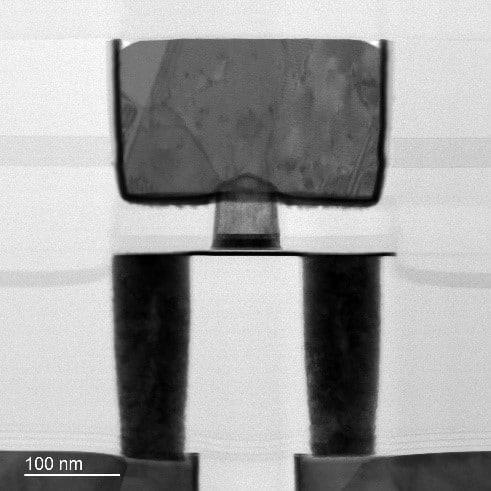

圖3 包含合成反鐵磁自由層的SOT-MRAM元件穿透電子顯微鏡(TEM)截面圖影像(發表於2024年IEEE國際電子會議)。

包含這層合成自由層的SOT-MRAM元件展現更優秀的寫入錯誤率(WER),首次達到10-6的目標規格。相較於包含傳統磁性自由層的元件,上述元件的資料保留時間從∆~50提升到~90。在讀取方面,還能在不影響SOT翻轉的情況下持續增加該元件的穿隧磁阻。此外,該複合材料自由層可以耐受高達400°C的溫度,同時維持其磁性特性,因而與後段製程相容。這層合成反鐵磁自由層也能降低SOT-MRAM對外部磁場擾動的敏感度。

在這項研究中,imec研究人員運用了微磁模擬來引導材料堆疊設計,帶來最佳成果。為了推進SOT-MRAM技術發展,結合模擬和實驗是必需的。

增強外部磁場干擾抵抗力

MRAM元件運作完全以電性控制,但外部磁場非常容易損害其元件性能。這種可靠度的問題引發了全球更廣泛的外部磁場抗擾力研究。本研究希望更瞭解所有的相關機制,並指引MRAM設計實現更佳的防護。目前也在發展依應用而定的多種標準,以量化MRAM對抗磁場的防護能力,指明已儲存資料仍在保護狀態下的磁場強度。

2024年IEDM上,imec提供首批實驗證據來說明,不只是外部磁場的強度,還有其磁性方向,都會對MRAM元件動態寫入外部磁場抗擾力產生負面影響,其跡象是寫入錯誤率的惡化。本研究在STT-MRAM元件上進行,但是其主要結論預計也適用於SOT-MRAM元件。這些實驗包含對直立磁性穿隧接面堆疊的不同角度施加多個外部磁場(介於4~40mT),並測量對寫入錯誤率產生的影響。據觀察,當磁場高於10mT,某些特定的外部磁場角度,會讓寫入可靠度明顯下降。

這些實驗可以與早期的理論發現相連。這些研究洞見將協助設計人員開發磁性穿隧接面堆疊,在現實應用中降低這些堆疊因角度不同,而出現寫入錯誤率損耗的負面影響。

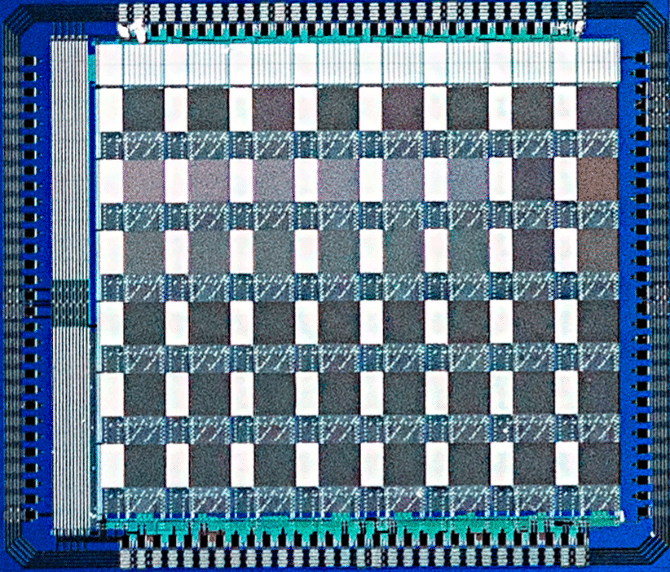

陣列層面:成功整合高度微縮的SOT-MRAM元件

還有一步尚待進行,那就是展示把改良後的SOT-MRAM元件整合到大型陣列及邏輯電路的可行性。2024年IEEE VLSI上,imec首次發表一款功能陣列,可作為不同SOT-MRAM配置特徵化的平台,這些配置已在元件層面證實運作良好。這種陣列因為可用於STT-MRAM特徵化,所以用途更多。

圖4 自旋軌道力矩(SOT)CMOS陣列影像(發表於2024年IEEE國際超大型積體電路技術研討會)。

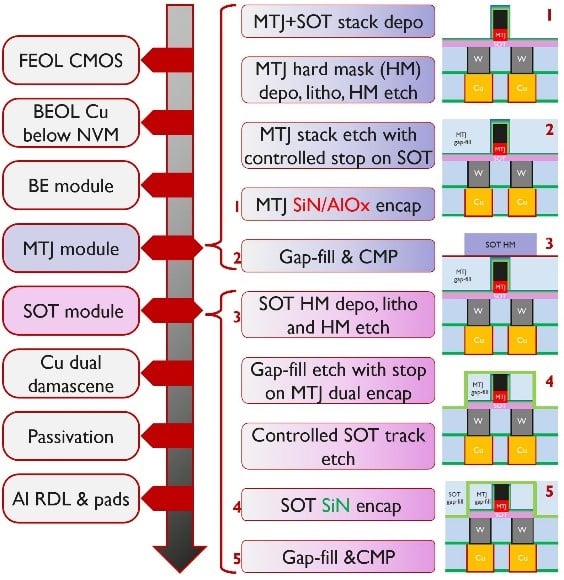

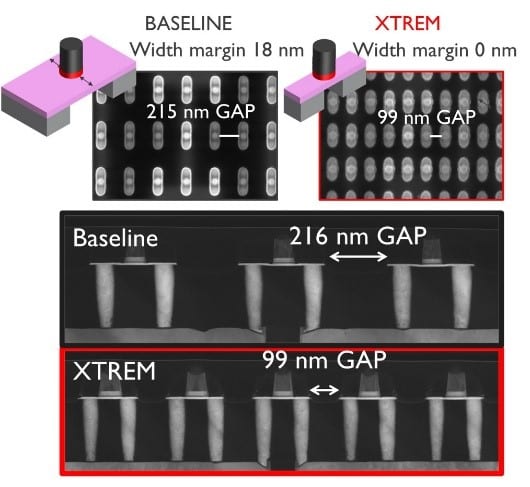

舉例來說,imec開始使用這種陣列來進行SOT-MRAM元件特徵化,這些元件透過縮小SOT軌道尺寸,已經微縮到最小程度。如先前所述,這些元件在元件層面的運作良好,展現在切換能量和重複讀寫次數方面的改善情形。元件整合的製程流程使得SOT軌道的圖形化必須在磁性穿隧接面柱成形之後進行。在極度微縮的元件中,SOT軌道寬度降到這些接面柱的直徑大小,這些柱型結構的側壁容易受到後續SOT圖形化步驟的影響,因而暴露和受損。

imec研究人員提出了一套創新的整合方案來解決此問題。利用氮化矽(SiN)和氧化鋁(ALOx)這兩種材料,有一種磁性穿隧接面柱的雙層封裝可以在SOT模組製程步驟中保護柱型結構,而不影響關鍵的性能參數,例如陣列層面的讀取窗口(Read Window)。

圖5 直立SOT-MRAM整合的製程流程,包含氮化矽(SiN)和氧化鋁(ALOx)雙封裝。

圖6 基線和極度微縮的SOT-MRAM元件的掃描式電子顯微鏡(SEM)俯視圖與穿透電子顯微鏡(TEM)影像(發表於2024年IEEE國際超大型積體電路技術研討會)。

把MRAM元件整合到大型陣列增添了複雜度:成千甚至上百萬的記憶體單元必須一致回應在周邊電路內部均勻運作的電晶體。imec目前在探索讓這些元件的變異性降低的方法。

SOT-MRAM可望扮演底層快取

SOT-MRAM元件一直被視為取代SRAM作為底層快取(LLC)的潛力候選技術。imec解決了一些剩餘挑戰,拉進這項技術與現實應用規格的距離。磁性穿隧接面材料堆疊的改良設計提升元件層面的翻轉可靠度,也增強對抗外部磁場影響的防護能力。一項有關外部磁場抗擾力的補充研究顯示了如何保護元件免於外部磁場影響的有用洞見。最後,功能陣列的展示呈現了推動業界採用這項技術的一大里程碑。

(本文作者任職於imec)