量子電腦很可能需要數百萬個量子位元(Qubit),才能準確執行其所承諾的轉型計算(Transformational Calculations)。不過,擴增量子位元的數量仍是一大障礙。先進CMOS製程可以達到晶圓級均勻度,且生產良率高,但由於不同的設計和操作條件,所以無法直接用來生產量子位元結構。imec研究人員近期在imec自家先進試驗製程廠房內的一條客製化12吋晶圓產線,展示矽量子點自旋量子與超導量子位元的成功整合。

對矽量子位元進行進階改良與特徵分析

接下來研究人員將進一步對這些量子位元進行特性分析並最佳化該製程,同時評估更大規模的量子位元陣列。其中一項重大問題仍是下降的電荷雜訊會對其他指標產生什麼影響?例如,雖然採用較厚的二氧化矽層(8~12奈米)有助於降低電荷雜訊,但也會增加量子點不同閘極之間的串擾,這會限制雙量子位元閘極的保真度。

更甚者,目前imec使用的製程是12吋晶圓電子束微影技術,因為其具備在每次設計迭代中改變設計的彈性。然而,電子束微影的產量有限,還有閘極對準精度方面的固有限制,這些都是其缺點。相較之下,主流CMOS製程使用的光學微影技術在減少對準誤差方面,還在持續改善。因此,從電子束改用光學微影(極紫外光微影),應會幫助推動這些製程的技術成熟度。

最後,升級單一量子位元和催化其成熟發展只是第一步。另一項挑戰是把這些量子位元整合到功能性陣列,並達成陣列之間的雙向傳輸。目前所用的交疊閘極結構可以完美展示單一量子位元和雙量子位元的運作,但未來持續擴增到數十或數百個量子位元時會遇到瓶頸。因此,研究團隊正在開發能擴充到更大型量子位元陣列的元件結構。這類架構需要經過製程改良和開發「量子後段製程」,因此,確保高保真度量子位元的相容性,會是這項研發工作的主要重點。

超導量子位元:從實驗室走進晶圓廠

儘管矽自旋量子位元因為具備較小尺寸、長相干時間和高整合密度的微縮優勢,以及與CMOS製程的高度相容性,因而極具長期發展的潛力,但超導量子電路才是現階段發展最為完善的技術平台。超導量子位元的能量狀態易於控制,加上其製作以量子位元得以相互作用為目標,而這種組合已成功展示了中型規模的量子處理器,能耦合數十到數百個超導量子位元。這些量子位元在實驗室環境中可實現長達數百微秒(µs)的長相干時間,和高達99.995%的單一量子位元閘極保真度。這兩者是量子運算的重要指標。

不過,多數超導量子位元仍是在實驗室內製作,這些場域所用的技術,例如遮蔽式蒸鍍和剝離製程。這類「溫和的」製程有助於產出特別乾淨的介面。這對超導量子位元的最關鍵組件–約瑟夫森接面(Josephson Junction, JJ)來說,尤其重要。

為盡可能達到最長的相干時間,組成該接面和量子位元其他部分的結構內有多種介面,務必要盡可能維持這些介面乾淨。就算是其中一個介面不幸出現單個原子等級的缺陷,也可能導致這顆量子位元失去相干性。不巧的是,這種製造技術與晶圓廠並不相容,而且通常很難擴大生產規模,所以量子運算不可或缺的大量量子位元,在生產方面遇到重重挑戰。

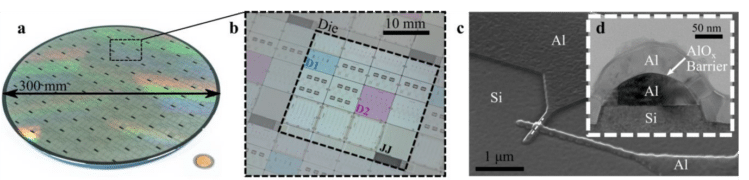

imec研究人員先前的研究已經展示了僅用CMOS相容的材料和實驗室技術來製作約瑟夫森接面的可行性(圖2)。這種交疊約瑟夫森接面的製作方式是交疊一個頂層電極和一個底層電極,兩者之間夾有一層絕緣體薄層。這些研究人員現在成功將這套製程轉移到完整的晶圓廠環境,在12吋矽晶圓上製造超導量子位元,專用採用光學微影和活性離子蝕刻技術,實現高達98.25%的量子位元生產良率。

圖3 (a)12吋晶圓的影像及(b)單顆晶粒的影像,強調約瑟夫森接面和量子位元次晶粒(Subdie)。(c)是單顆交疊約瑟夫森接面的傾斜穿透電子顯微鏡(TEM)圖及(d)該接面的穿透電子顯微鏡截面圖。

這些量子位元展現超過100微秒的相干時間,極為出色,因而確定了運用與晶圓廠相容的製程步驟,可以製出足夠純淨的介面品質。此外,imec團隊也發現這種約瑟夫森接面具備卓越的穩定度及老化表現,甚至比實驗室製造還要好得多。利用遮蔽式蒸鍍製造的約瑟夫森接面,通常會出現明顯的老化現象:接面隨著時間增加電阻,這顯示該接面在量子位元內或降溫時的材料表現。這些室溫電阻可能隔一天就會變化幾十個百分率,但這種新型交疊約瑟夫森接面卻高度可靠,老化程度只有個位數百分率。

超導量子位元未來方向:強化製程控制和探索3D

研究人員首次建立了一套用於12吋矽晶圓的製程,達到高相干性和跨晶圓產量。下一步是強化製程控制,處理個別量子位元之間和晶圓之間所觀測到的變異性。另外,未來也會進一步探索多種表面處理、清洗技術和新型材料,以持續改良介面,進而提升量子位元的相干時間。

更長遠來看,當擴充到數十個量子位元時,3D整合技術將是首要之務。首先是連接量子位元。目前像是空橋(Air Bridge)這類解決方案並不理想,因為會引發串擾和表面損耗。另一個重點工作是增加量子位元的數量。超導量子位元相對於電晶體來說,是十分龐大的元件,其尺寸可達毫米等級,而且這些元件無法在2D平面大幅微縮。就算是轉移到晶圓廠製造可以取得最先進的3D技術,但3D整合依舊錯綜複雜。其中一個主要障礙是在堆疊時保護約瑟夫森接面。任何在約瑟夫森接面製程之後進行的3D處理技術,都不能影響或破壞該接面。例如,熱預算被限制在200°C,就是一個需要克服的問題。現有製程的溫度高出這個數字許多。

業界主流製程亦可用於量子位元製造

imec透過完整的業界12吋晶圓製造來展示半導體與超導量子位元的成功整合,實現可再現和高產量的量子位元。這些成果確認了業界採用的成熟製造技術,也可以運用在量子技術的開發上。

為了讓基於成千上百個量子位元的系統得以運作,這是必要的技術重大升級。imec正在為了擴增具備頂尖性能的量子位元而進一步改良製程,並改良連接這些量子位元的必要技術。

(本文作者任職於imec)