大語言模型(LLM)帶動了雲端伺服器的發展,但應用落地及商業價值的回收,端賴邊緣運算的普及,例如AI手機、PC、汽車、監控與其他高價值的物聯網終端等。這類可能應用AI的高階終端系統具有極大的發展潛能,但邊緣運算應用的客觀條件與性價比需求,使雲端使用的昂貴先進邏輯及標準化的高頻寬記憶體與封裝技術,在經濟層面上很難應用在邊緣裝置的晶片上。

因此,聯電聯合供應鏈夥伴推出的晶圓對晶圓(W2W) 3DIC技術,搭配聯電夥伴的高頻特規DRAM,以滿足邊緣運算裝置運行LLM的需求,將能為半導體市場添上另外一股成長薪柴。

LLM帶動雲端應用高速成長 邊緣運算仍須突破效能瓶頸

LLM興起,帶動生成式AI技術在各種應用情境中百花齊放,使得雲端服務供應商(Cloud Service Provider, CSP)莫不在於處理器與AI GPU,NPU,記憶體等晶片產品發展上加大研發與投資力道。所以自2023年開始,不論是在先進製程或是先進封裝領域的發展上,都呈現了相當驚人的成長。

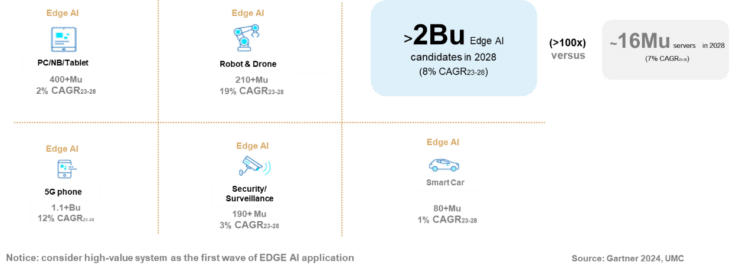

隨著生成式AI逐漸在各種應用情境發酵與落地,運行生成式AI與LLM的需求,自然也就不僅止於AI PC、手機與雲端服務應用。許多邊緣運算與垂直應用場景,若能搭配適當的LLM,同樣可能發揮相當大的潛能,為人類帶來很多方便。根據Gartner預估,單就機器人與無人機在2028年市場規模,就高達2億1千萬台以上,安全監控攝影機的數量也高達1億9千萬支,這些皆是AI邊緣運算的可能機會(圖1)。

圖1 至2028年,潛在的邊緣AI裝置將超過20億台

在處理LLM與生成式AI的工作時,處理器與記憶體之間的資料搬運效率的高低,往往是生成式AI使用體驗表現好壞的重要關鍵之一。因此,在雲端伺服器與資料中心領域,衍生了2.5D 與HBM相關技術來解決資料搬運效率不佳的問題,但這種作法的成本過於高昂,並不適用於邊緣運算。在雲端服務應用場景十分普遍的AI加速晶片搭配高頻寬記憶體(HBM)設計,其最終價格動輒超過兩萬美元以上;而且其效能雖然傑出,但體積跟功耗實在不適合邊緣運算的需求。

因此,針對邊緣運算應用,像是AI PC與AI手機,其處理器只能採用搭配LPDDR5/5X記憶體的設計。其價格雖然落在約略在數百美元的範圍內,但其頻寬的規格以及頻寬使用效率,對於LLM邊緣運算應用來說,往往又顯得不足。

W2W 3DIC創造性價比甜蜜點

也因此,針對邊緣應用場景開發成本合宜的處理器,滿足LLM邊緣運算的需求,成了國際大廠與新創業者所思考探索的發展途徑,從而促使了聯電利用既有製程,與客戶合作,共同探索W2W 3DIC堆疊技術的可能性。同時,聯電也與記憶體廠商、IC設計、封裝與電子設計自動化(EDA)設計軟體等重要供應鏈廠商合作,就各種供應鏈環節面向展開,來滿足客戶邊緣AI運算的需求,並兼顧性價比表現。

聯電所提供的W2W 3DIC技術,主要是由聯電提供邏輯製程晶圓,其製程範圍主要是以28nm至12nm為主,而記憶體廠商則是提供搭載特規超高頻寬元件架構的記憶體晶圓,將兩種不同屬性的晶圓以聯電混合鍵合(Hybrid Bonding)技術加以堆疊。由聯電夥伴記憶體廠商所開發的特規超高頻寬元件架構,比傳統的記憶體擁有更多I/O數,並且可以透過聯電的Hybrid Bonding技術,減少搬運資料時的耗電量,可以有較低的能源消耗,並同時兼顧高頻寬與小尺寸的特性。

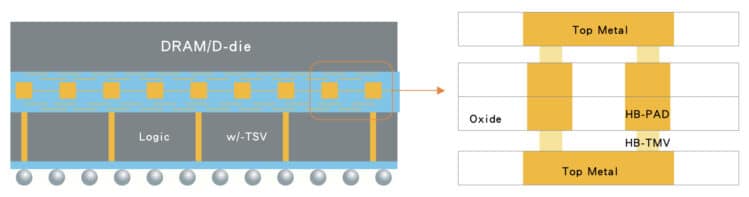

Hybrid Bonding技術讓兩片不同功能的晶圓可以經由Hybrid Bonding的焊墊(Pad)直接連結,進而縮短資料傳輸路徑並降低能耗。同時,由於是基於半導體級的製程技術,因此焊墊的間距大幅縮小,使得在相同的面積下,I/O連接密度得到大幅提升,讓傳輸頻寬明顯增加(圖2)。這種作法可以因應目前絕大多數需要一定運算效能,且同時兼具低功耗的邊緣運算應用場景需求。

圖2 透過W2W Hybrid Bonding技術,將記憶體與邏輯晶圓進行3D堆疊以提高效能與降低能耗,落實邊緣AI終端裝置所需硬體需求

在完成兩種不同屬性的晶圓3D堆疊接合之後,邏輯晶圓與記憶體晶圓之間便可以進行資料傳輸。再交由聯電的封裝夥伴廠商處理堆疊完成的晶圓切割、封裝和測試工作,並以透過預先建置好的矽穿孔(TSV)技術對外部系統產生電氣連結。

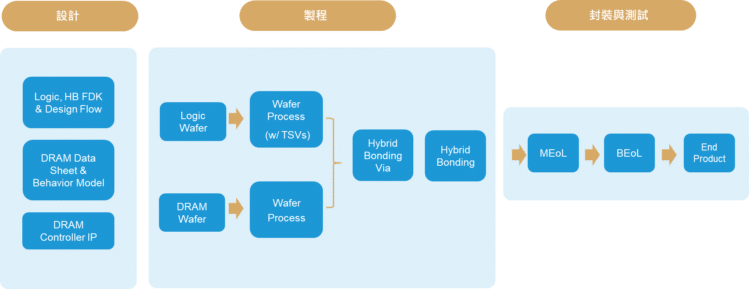

晶片設計方面,EDA 設計軟體公司則是以晶片設計的角度,提供驗證完整的W2W 3DIC設計流程、提取TSV等相關特性與簽核認證。IC設計服務公司則提供全面的3D先進封裝一站式服務,及記憶體IP和ASIC晶片設計服務。以此,聯電與夥伴供應鏈廠商建構起自晶片設計、晶圓製造與堆疊,再到切割與封測的完整 W2W 3DIC的設計與製造流程(圖3)。目前合作進行排障驗證工作已有一年多的時間,並據此與國內外不同的客戶進行早期的合作開發討論。

圖3 聯華電子與夥伴啟動W2W 3DIC專案

生成式AI走向邊緣場景 3DIC是關鍵

總結來看,生成式AI浪潮為邊緣運算帶來更多的想像空間,但在成本與效能需求之間的平衡,對多種垂直應用場景來說相當重要。目前,市場對邊緣運算處理器的發展需求火熱,而聯電與主要供應鏈合作,打造W2W 3DIC一條龍的設計與製造流程,希望進一步提升邊緣運算處理器的性價比與效能,實現高頻寬、低功耗與小尺寸的設計,也為AI半導體的發展再添成長動能。

(本文作者為聯華電子市場行銷處副處長)